Par Julien Le Sech,

mardi 26 juin 2012.

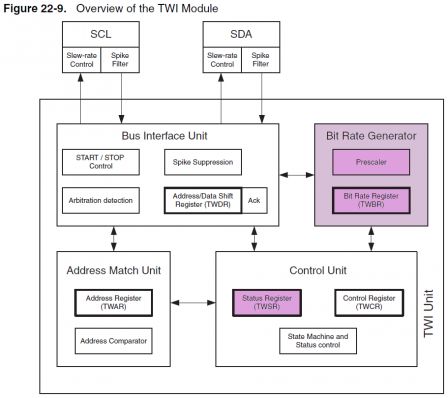

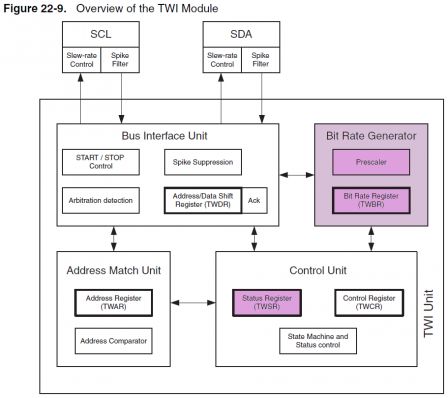

La plupart des microcontrôleurs megaAVR d'Atmel, dont l'ATmega328P, dispose d'un module I2C ou TWI. Celui-ci se décompose en plusieurs sous ensembles ou units :

- Bit Rate Generator Unit ;

- Bus Interface Unit ;

- Address Match Unit ;

- Control Unit.

Cet article se focalise sur le Bit Rate Generator Unit et propose d'apprendre à le configurer sur un ATmega328P. Par conséquent, il n'a pas pour objectif de proposer une bibliothèque TWI complète, cette dernière étant en cours de développement.

Le Bit Rate Generator Unit contrôle la période du signal SCL en mode maître ou master. Cette période est déterminée par la configuration du bit rate dans le registre TWBR et du prescaler dans le registre TWSR.

Le bit rate est le débit binaire, c'est à dire le nombre de bits par seconde envoyés ou reçus sur le bus TWI. Le prescaler est un diviseur de fréquence. Il permet de diviser la fréquence CPU pour atteindre la fréquence SCL du bus TWI.